How AMD 3D V-Cache can increase Ryzen performance by up to 25 percent - ullrichdarpre

AMD said Monday evening at Computex 2021 that it has evolved its chiplet architecture into 3D chiplets, specifically what IT calls 3D V-Cache technology. By itself, the technology promises carrying out gains for its Ryzen and Epyc processors that can touch 25 per centum.

AMD has successful "nifty progress" along its 3D chiplet technology, and should debut it in its "highest-closing products" by the oddment of 2021, AMD gaffer executive Dr. Lisa Su aforesaid during a Computex keynote destination.3D V-Cache allows AMD to take a Ryzen 5000 versatile processor and connect a 64MB SRAM cache directly on top of it.

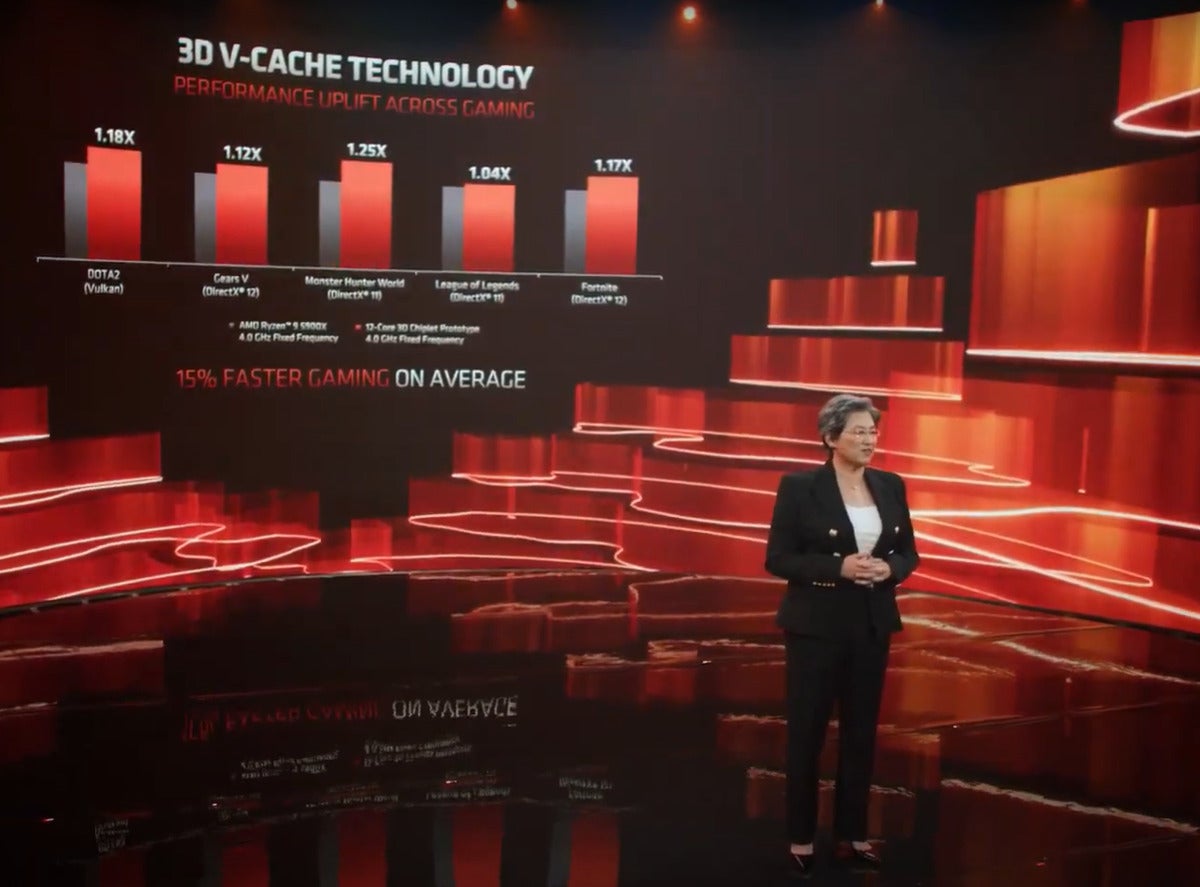

Su showed off a Ryzen 9 5900X, AMD's fastest gaming CPU, and then compared information technology to a prototype 5900X with 3D V-Cache committed to it. In Xbox Game Studios'Gears 5,figure rates built by 12 percent. In separate games, also using an identically clocked 5900X, performance enlarged 4 to 25 percent, for an average of 14 percent, Su aforesaid.

YouTube / AMD

YouTube / AMD AMD's Dr. Lisa Su provided benchmarks showing how the prototype 3D V-Cache can dramatically improve play performance.

Stacked chips sound like the future

This may wholly sound familiar. In 2018, Intel began showing off how its Foveros technology allowed for stacking its CPU logic on top of one another. That allowed Intel to create the temporary Lakefield processor, merely also the upcoming, higher-performing Alder Lake chip, which Intel displayed at Computex in both desktop and mobile versions.

YouTube / AMD

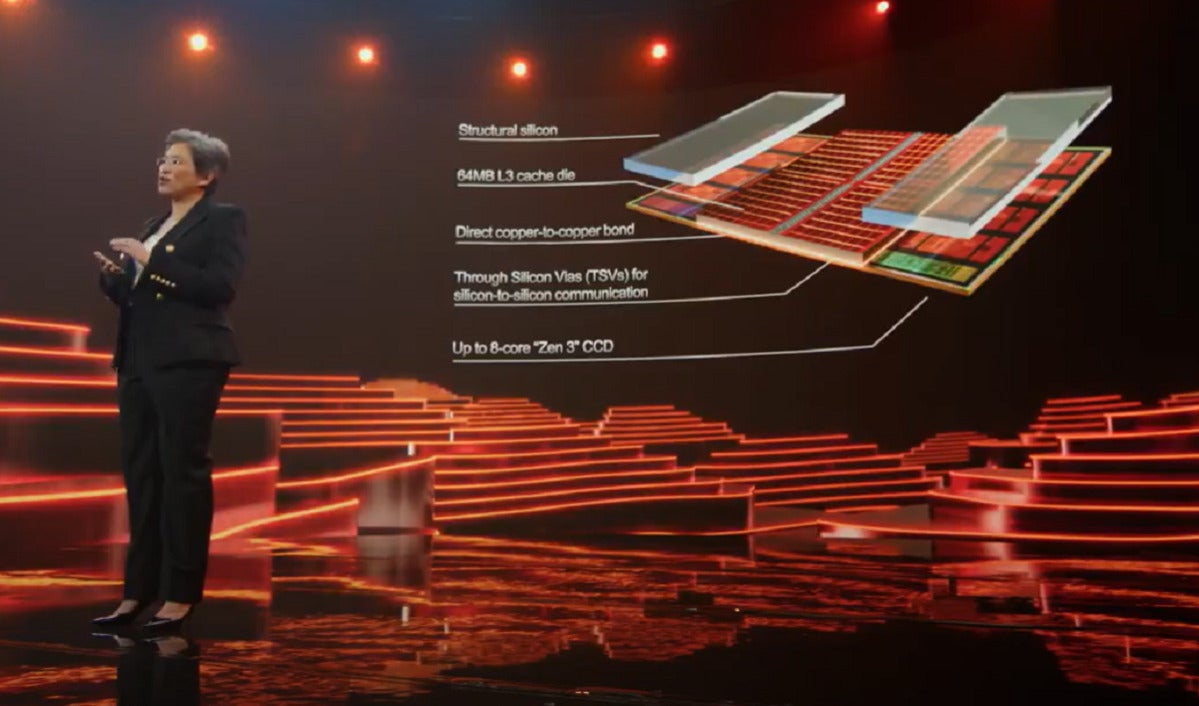

YouTube / AMD AMD CEO Dr. Lisa Su explains 3D V-Cache in her Computex presentation.

According to Tirias Search psychoanalyst Kevin Krewell, still, AMD's carrying out of 3D stacking engineering is different. AMD is using through-silicon via technology from TSMC, its foundry partner, similar to the engineering used by remembering makers to stack DRAM and NAND flash on top of one another. IT has better power and bandwidth characteristics than Foveros, but it's unknown how well it sack be factory-made.

"AMD is using the technical school to gravel an extra ~12 percent performance boost for its CPUs by adding more L3 stash," Krewell said via twinkling substance. "This technology can also be used in EPYC servers."

Placing a biggish cache directly adjacent to the Central processing unit derriere have significant performance advantages. Processors postulate to ask for instructions, and storing them in an easy approachable cache—versus seeking them impermissible in system memory—behind be an elementary way to increase system performance. Just baking that cache into the processor pass away introduces more opportunity for chip defects. In a worst-casing scenario, the entire chip could be rendered useless.

Adding the cache as a branch out die and and so stacking it saves space and cost, while quieten maintaining the bandwidth vantage and adding gobs of available cache. For example, Su same its prototype soldered SRAM to each AMD CCD, for a full of 192MB of SRAM cache. The available level-3 cache on today's 5900X is sensible 64MB, or a third of the 3D V-Cache image.

YouTube / AMD

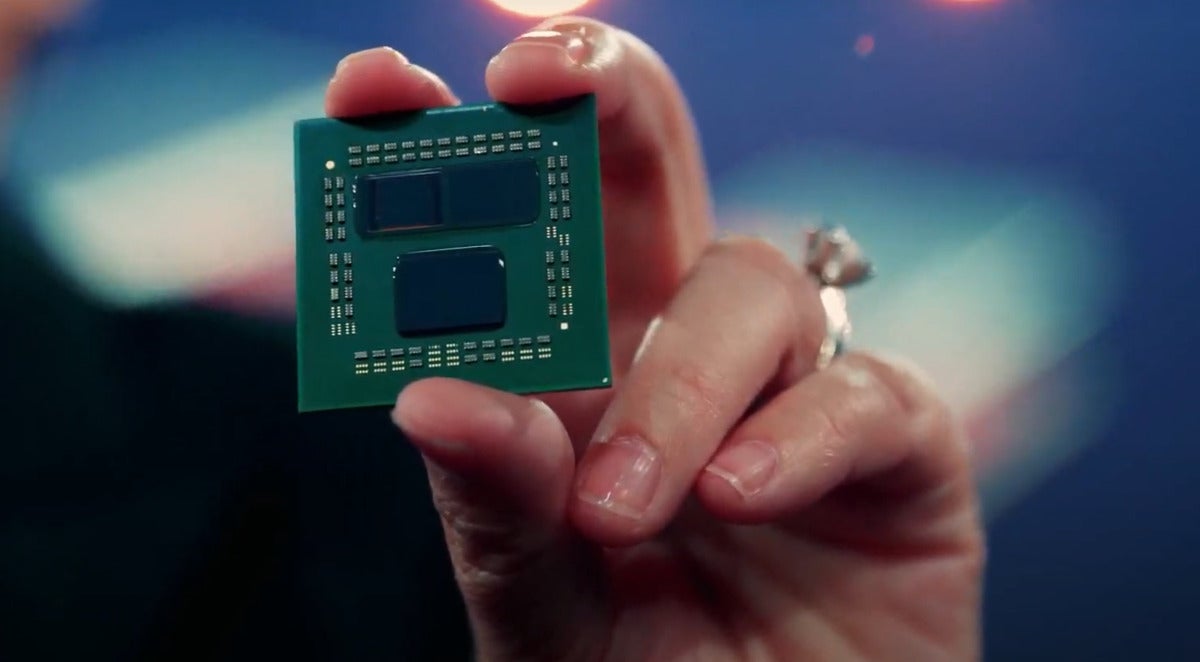

YouTube / AMD AMD's Su holds up the prototype 3D V-Hoard chip.

Following AMD's multichip modules and chiplet go up, Su called 3D chiplets the "next Brobdingnagian step forward." Placing the additional silicon on top of the Processor die triples the available cache. TSMC's through-silicon vias (or on-chip "wires") allow the CPU and cache to talk to one some other at more than 2 TBps of bandwidth, Su same. Su also said that AMD's kick the bucket-to-die approach uses direct copper connections, not solder bumps. That's an indirect criticism of Intel's Foveros approach, which uses microbumps and thence consumes more power and provides to a lesser extent bandwidth, Krewell noted.

For straightaway, that also means that AMD can't easily reproduce Intel's Alder Lake approach. Along the other hand, it might non topic, as AMD can clear performance gains in some its Ryzen and Epyc processors, and possibly its GPUs. Now, the question is: Which of AMD's chips will be endowed with 3D V-Memory cache?

Source: https://www.pcworld.com/article/394646/how-amds-3d-v-cache-can-increase-ryzen-performance-by-up-to-25-percent.html

Posted by: ullrichdarpre.blogspot.com

0 Response to "How AMD 3D V-Cache can increase Ryzen performance by up to 25 percent - ullrichdarpre"

Post a Comment